## A Technique for Improving the Distortion of GaAs Variable Attenuator IC Using Squeezed-Gate FET Structure

Kazuo Miyatsuji, Hidetoshi Ishida, Takeshi Fukui and Daisuke Ueda

Matsushita Electronics Corporation, Electronics Research Laboratory

1-1 sawai-cho, Takatsuki, Osaka 569-11, Japan

### Abstract

This paper describes a novel technique for improving the distortion of the GaAs attenuator IC using squeezed-gate structure of MESFETs. We found that the distortion was originated from the steep cutoff  $Id$ - $Vgs$  curve of conventional FETs. To obtain smooth cutoff characteristics, we devised the squeezed-gate structure where the FETs with different threshold voltages are connected in parallel making use of the short channel effect. Fabricated IC shows 10 dB reduction of the 3rd order intermodulation distortion by optimizing the ratio of the gate widths.

### Introduction

There has been a growing demand for RF variable attenuators to control transmitting power of the digital cellular phones. Such attenuators are placed at the input of the power amplifier to reduce excess power consumption when the base station is near by. Although monolithic GaAs attenuator IC has an advantage of almost zero power dissipation and small package size [1-4], it shows a quite large distortion which seriously degrades the bit error rate.

In this paper, we report on a novel technique for improving the distortion of the GaAs attenuator IC

using squeezed-gate structure of MESFETs. We found that the distortion was originated from the steep cutoff  $Id$ - $Vgs$  curve of conventional FETs. To obtain smooth cutoff characteristics, we devised the squeezed-gate structure where the FETs with different threshold voltages are connected in parallel making use of the short channel effect. Fabricated IC shows 10 dB reduction of the 3rd order intermodulation distortion by optimizing the ratio of the gate widths.

### Squeezed-Gate FET

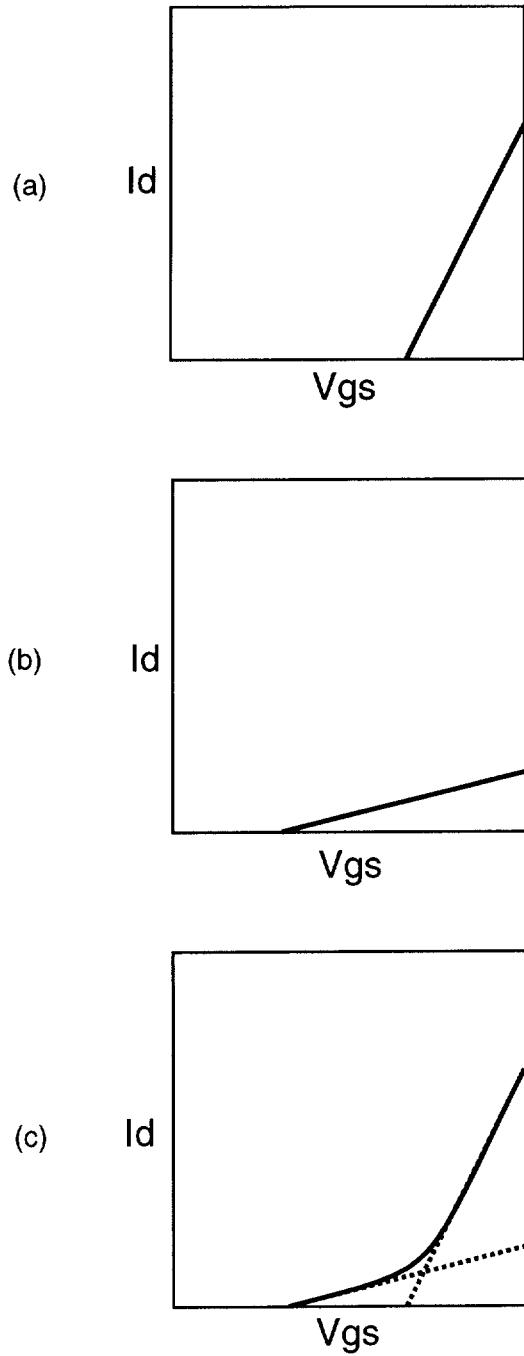

Conventional GaAs FET used as variable impedance device is designed to have low on-resistance to obtain low insertion loss. Such a FET shows a steep  $Id$ - $Vgs$  curve as shown in Fig. 1(a). This steep cutoff characteristics causes large distortion especially when the FET is biased at around the threshold voltage. This is because the gate voltage is modulated by the input RF signal due to the parasitic capacitances  $C_{gd}$  or  $C_{gs}$ . The FET with deeper threshold voltage and smaller gate width shows a low-pitched cutoff characteristics (Fig. 1 (b)), however, the on-resistance is increased resulting in degrading the insertion loss. The parallel connection of these two FETs will show smooth cutoff characteristics without increasing the on-resistance as shown in Fig. 1 (c).

**Figure1.** Schematic of the  $Id$ - $Vgs$  characteristics.

- (a) conventional FET.

- (b) FET with deeper threshold voltage.

- (c) parallel connection of (a) and (b).

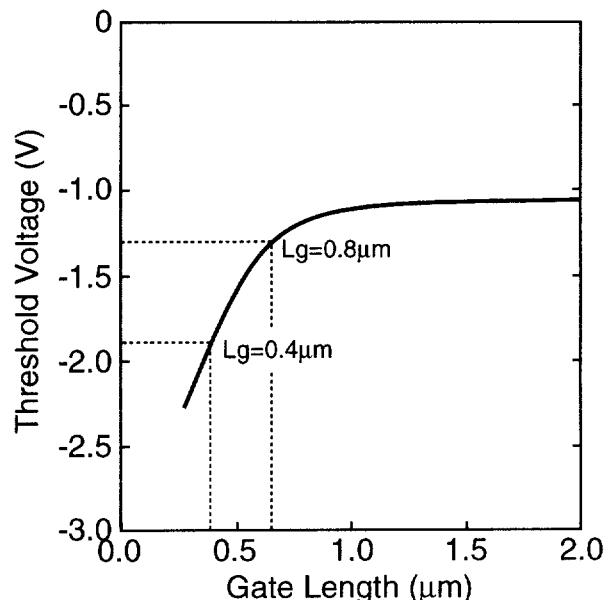

**Figure2.** An Example of the short channel effect of the GaAs MESFET.

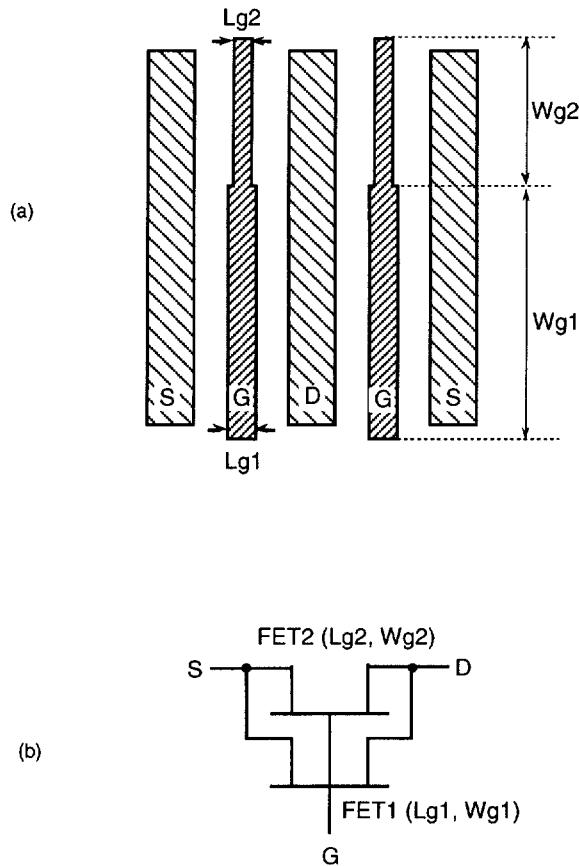

As well-known, there exists the short channel effect of the GaAs MESFET as shown in Fig. 2. Utilizing this short channel effect, we devised the squeezed-gate FET structure as shown in Fig. 3 (a). This configuration is equivalent to the parallel connection of FETs that have two different threshold voltages (Fig. 3 (b)). It should be noted that this favorable characteristics is obtainable only by mask layout of the gate patterning without using complicated epi structure or fabrication process.

**Figure 3.** Schematic of the squeezed-gate FET structure (a) and its equivalent circuit(b) .

### Attenuator IC Fabrication

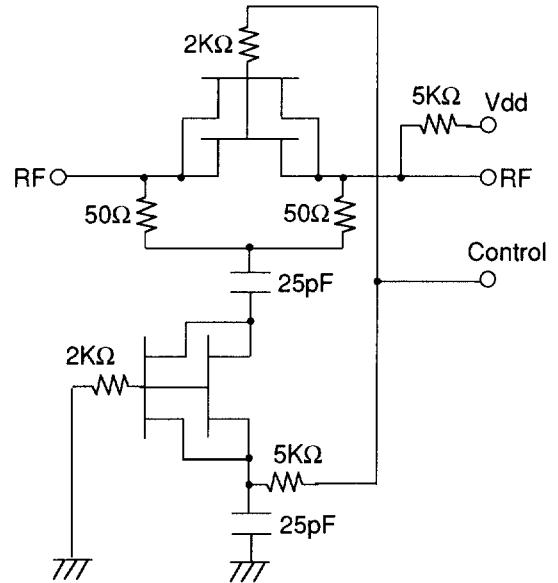

To confirm the improvement of the distortion by the squeezed-gate structure, we designed and fabricated attenuator IC. Figure 4 shows the designed variable attenuator circuit using the squeezed-gate FET's. Two capacitors as large as  $25\text{pF}$  enable this bridged-T type attenuator circuit to operate with a single positive control voltage.[4,5]. To integrate such large capacitors on a GaAs substrate, on-chip BST (Barium Strontium Titanate) capacitor technology [6-7] was employed.

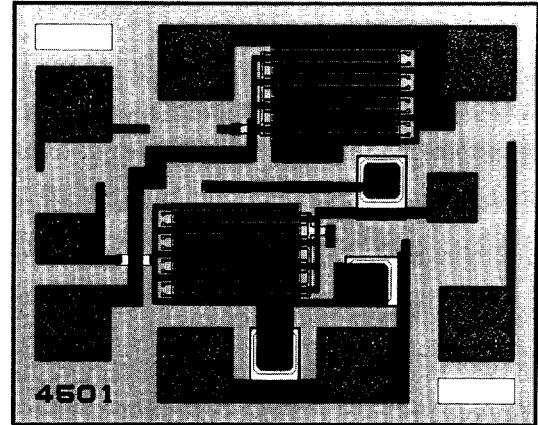

The chip photograph is shown in Fig. 5. The chip size is  $0.58\text{ mm} \times 0.7\text{ mm}$ . The lengths of the squeezed-gate ( $Lg1$  and  $Lg2$  in Fig. 1 (a)) are 0.4 and  $0.8\text{ }\mu\text{m}$ . The total gate width ( $Wg1 + Wg2$ ) of each FET is 1.2 mm.

**Figure 4.** Designed variable attenuator circuit using squeezed-gate FETs.

**Figure 5.** Chip micro photograph of the fabricated attenuator IC

## Measurement Result

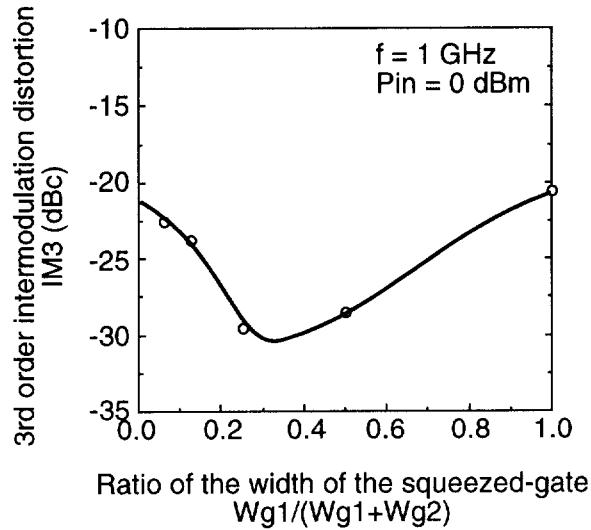

The 3rd order intermodulation distortion (IM3) of the fabricated IC was measured by using the 2-tone method. Figure 6 shows the measured IM3 as a function of the ratio of the width of the squeezed-gate. The IM3 shows a minimum value of -31dBc at the gate-width ratio of 0.35. This value is 10dB lower than that of the conventional constant gate-length FET.

**Figure 6.** The 3rd order intermodulation distortion (IM3) of the fabricated IC as a function of the width ratio of the squeezed gate.

## Conclusion

We have developed a novel technique for improving the distortion of the GaAs attenuator IC using squeezed-gate structure of MESFETs, where two different length of the gates are connected in each finger. Owing to the smooth cutoff characteristics of the Id-

$V_{gs}$  curve, the 3rd order intermodulation distortion shows 10 dB improvement from the conventional FET structure. This technique contributes to design of low-distortion GaAs attenuator IC for digital mobile communication systems such as TDMA or CDMA.

## Acknowledgement

The authors would like to thank Kazutsune Miyanaga for his contribution in the GaAs IC fabrication. The authors are also very grateful to Dr. Kunio Itoh and Dr. Gota Kano for their constant encouragement through this work.

## Reference

- [1] Lizama, K., et al., "1-6 GHz GaAs MMIC Linear Attenuator with Integral Drivers," Digest Paper of IEEE Microwave and Millimeter-Wave Monolithic Circuits Symposium, pp. 105-107, 1987.

- [2] Maoz, B., "A Novel Linear Voltage Variable MMIC Attenuator," IEEE Trans. Microwave Theory Tech., Vol. 38, No. 11, pp. 1675-1683, 1990

- [3] Sun, H., J., et al., "A 2-20GHz GaAs MESFET Variable Attenuator Using A Single Positive External Drive Voltage," Conf. Proc. 19 th Eur. Microwave Conf., pp. 1270-1275, 1989.

- [4] Miyatsushi, K., and Ueda, D., "A Low Distortion GaAs Variable Attenuator IC for Digital Mobile Communication System," ISSCC Digest of Technical Papers, pp. 42-43, Feb., 1995.

- [5] Miyatsushi, K., and Ueda, D., "A GaAs Single Voltage Controlled RF Switch IC," Asia Pacific Microwave Conference Proceedings vol. I, pp. 135-138, 1994.

- [6] Miyatsushi, K., et al., "A GaAs High-Power RF Single-Pole Double-Throw Switch IC for Digital Mobile Communication System," ISSCC Digest of Technical Papers, pp. 34-35, Feb., 1994.

- [7] Ueda, T., et al., "GaAs MMIC Chip-sets for Mobile Communication System with On-chip Ferroelectric Capacitors," Integrated Ferroelectrics, vol. 7, pp. 45-60, 1995.